限られた電力で動作する極低電圧動作情報処理集積回路

CMOS

サブスレショルド動作

PWM演算回路

AD-PLL

研究シーズの特徴・独自性

集積回路の微細化により動作速度は向上するが、リーク電流が増加してしまうため、消費電力が思うように下がらない。その問題を解決するために、リーク電流の一種であるサブスレッショルド電流を用いた極低電圧回路の研究を行っている。強反転領域の1/100で数nA~数百nAオーダーである。この電流で回路を駆動することで、さらなる低消費電力化が実現できる。

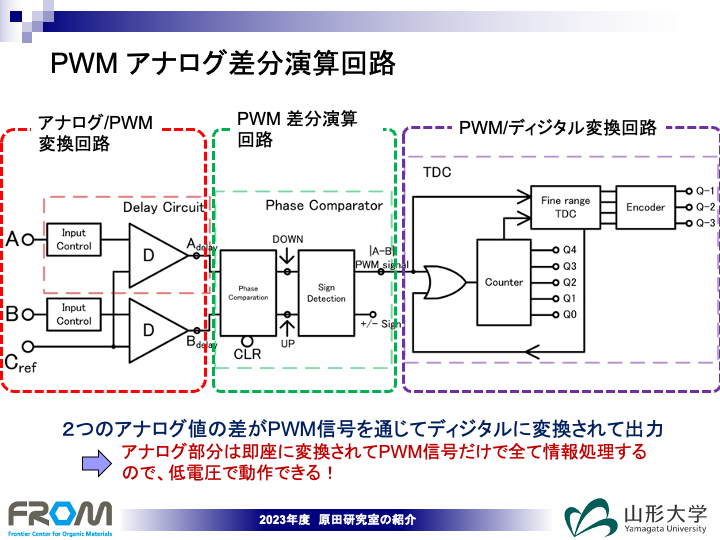

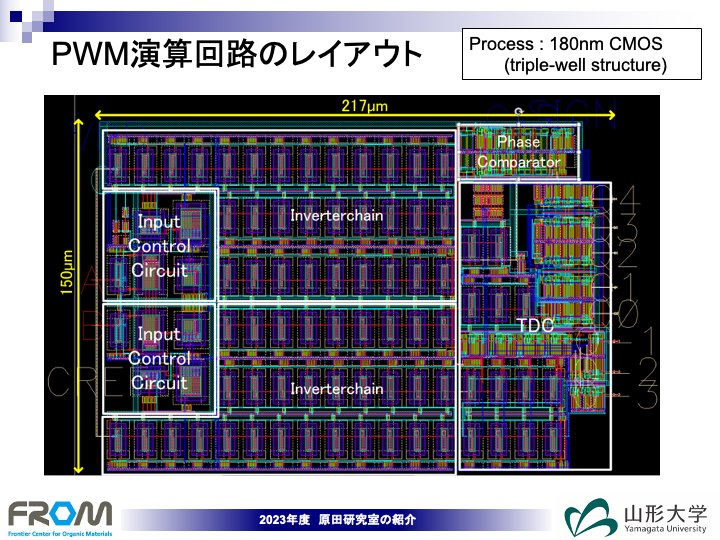

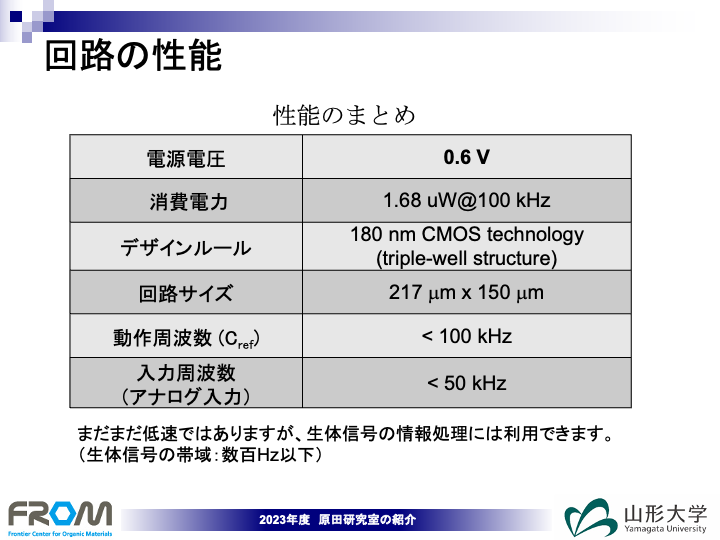

サブスレッショルド電流を用いた信号処理方式はアナログ方式とデジタル方式があるが、アナログ信号の連続性とデジタル信号におけるノイズ耐性を合わせ持つパルス幅変調(PWM)信号を利用し、PWM信号を用いた信号処理集積回路を実現することで、回路素子数を抑えながらも低電圧化でき、かつ問題となるノイズに強い回路を構成することができる。また、PWMだけでなく、full-digitalなPLL(AD-PLL)についても、サブスレショルド領域で設計・動作することで、消費電力低減が可能となる。これにより、IoTデバイス向けの情報処理回路とクロック生成回路の低消費電力化による長期動作が実現できる。

サブスレッショルド電流を用いた信号処理方式はアナログ方式とデジタル方式があるが、アナログ信号の連続性とデジタル信号におけるノイズ耐性を合わせ持つパルス幅変調(PWM)信号を利用し、PWM信号を用いた信号処理集積回路を実現することで、回路素子数を抑えながらも低電圧化でき、かつ問題となるノイズに強い回路を構成することができる。また、PWMだけでなく、full-digitalなPLL(AD-PLL)についても、サブスレショルド領域で設計・動作することで、消費電力低減が可能となる。これにより、IoTデバイス向けの情報処理回路とクロック生成回路の低消費電力化による長期動作が実現できる。

産学連携の可能性

本研究室では、消費電力の効果的な削減方法として、ナノアンペアという微小な電流、つまりリーク電流を、集積回路を動かす電力として使ってしまおうというコンセプトのもと、日々研究しております。また、ただ単にナノアンペアで動作させるだけでなく、アナログ振幅情報を時間軸情報に変換し、さらにオペアンプのような差動演算とディジタルへの変換も兼ねたPWM(パルス幅変調)差分演算回路といった演算回路も研究しております。この回路は、今日のIoTを支えるセンサ直近の低電力情報処理回路の実現に貢献できると期待しております。